集成電路CAD設(shè)計(jì)中的芯片焊盤(pán)與版圖布局

集成電路(IC)設(shè)計(jì)是現(xiàn)代電子工業(yè)的核心環(huán)節(jié),而CAD(計(jì)算機(jī)輔助設(shè)計(jì))工具的應(yīng)用使得這一過(guò)程更加高效和精確。在集成電路設(shè)計(jì)中,芯片焊盤(pán)和版圖布局是兩個(gè)關(guān)鍵組成部分,它們直接影響到芯片的性能、可靠性和制造成本。

1. 集成電路CAD設(shè)計(jì)概述

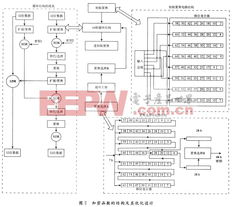

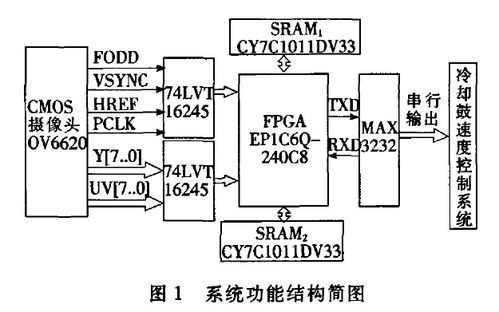

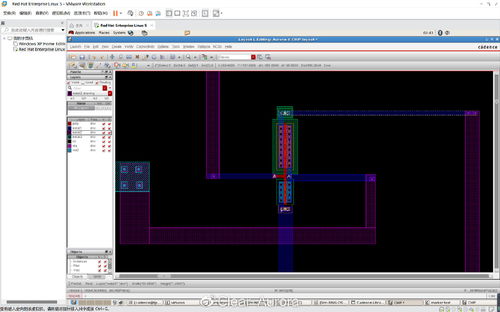

集成電路CAD設(shè)計(jì)利用專(zhuān)業(yè)軟件(如Cadence、Synopsys等)進(jìn)行電路仿真、布局和驗(yàn)證。它涵蓋了從邏輯設(shè)計(jì)到物理實(shí)現(xiàn)的整個(gè)流程,包括原理圖輸入、模擬仿真、布局規(guī)劃、布線以及設(shè)計(jì)規(guī)則檢查(DRC)和版圖與電路圖一致性檢查(LVS)。CAD工具不僅提高了設(shè)計(jì)效率,還減少了人為錯(cuò)誤,確保芯片符合制造要求。

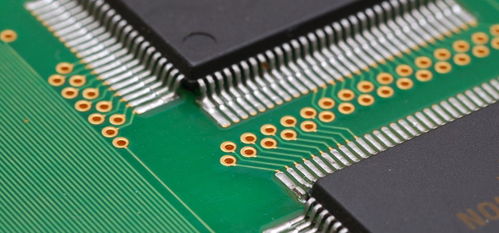

2. 芯片焊盤(pán)設(shè)計(jì)

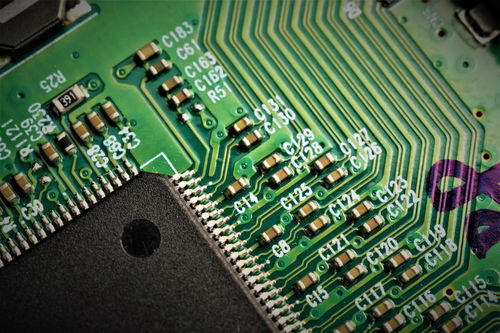

芯片焊盤(pán)是集成電路與外部電路連接的接口,通常位于芯片邊緣。它們負(fù)責(zé)傳輸信號(hào)、電源和接地。焊盤(pán)設(shè)計(jì)需要考慮多個(gè)因素:

- 尺寸和形狀:焊盤(pán)的大小必須符合制造工藝的規(guī)則,同時(shí)確保良好的電接觸。常見(jiàn)的形狀包括矩形或圓形。

- 材料選擇:通常使用鋁或銅等導(dǎo)電材料,以降低電阻和防止腐蝕。

- 布局優(yōu)化:焊盤(pán)應(yīng)均勻分布,避免信號(hào)干擾和熱集中問(wèn)題。在高速電路中,還需考慮阻抗匹配和信號(hào)完整性。

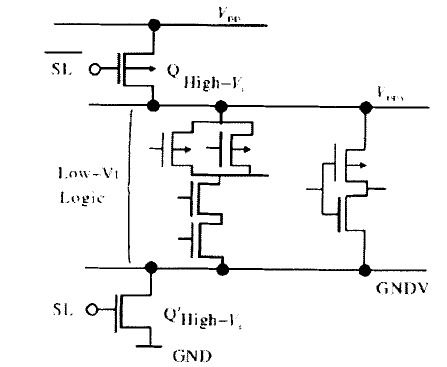

- 可靠性:設(shè)計(jì)時(shí)需預(yù)留保護(hù)結(jié)構(gòu),如靜電放電(ESD)保護(hù)電路,以防止外部損壞。

3. 版圖布局設(shè)計(jì)

版圖布局是將電路邏輯轉(zhuǎn)化為物理結(jié)構(gòu)的過(guò)程,涉及晶體管、電阻、電容等元件的放置和互連。其目標(biāo)是實(shí)現(xiàn)高性能、低功耗和小面積:

- 布局規(guī)劃:首先確定芯片的整體結(jié)構(gòu),包括核心區(qū)域、焊盤(pán)區(qū)域和電源分布。通過(guò)分層設(shè)計(jì)(如金屬層堆疊)來(lái)優(yōu)化布線。

- 元件放置:關(guān)鍵元件(如時(shí)鐘生成器)應(yīng)優(yōu)先放置,以減少延遲和功耗。布局需考慮熱管理和信號(hào)路徑最短化。

- 布線設(shè)計(jì):使用CAD工具自動(dòng)或手動(dòng)布線,確保連接符合設(shè)計(jì)規(guī)則。多層金屬布線可提高密度,但需避免串?dāng)_和電遷移問(wèn)題。

- 驗(yàn)證與優(yōu)化:通過(guò)DRC和LVS檢查,確保布局無(wú)制造錯(cuò)誤。同時(shí),進(jìn)行寄生參數(shù)提取和時(shí)序分析,以?xún)?yōu)化性能。

4. 集成設(shè)計(jì)與挑戰(zhàn)

在集成電路CAD設(shè)計(jì)中,焊盤(pán)和版圖布局需協(xié)同工作。例如,焊盤(pán)的位置會(huì)影響版圖的整體布線,而版圖密度可能限制焊盤(pán)數(shù)量。隨著工藝節(jié)點(diǎn)縮小(如7nm以下),設(shè)計(jì)面臨更多挑戰(zhàn):

- 功耗與散熱:高集成度導(dǎo)致功率密度上升,需在布局中引入散熱結(jié)構(gòu)。

- 信號(hào)完整性:高速信號(hào)易受噪聲影響,要求焊盤(pán)和布線采用屏蔽技術(shù)。

- 制造變異:先進(jìn)工藝中,版圖需考慮工藝偏差,通過(guò)冗余設(shè)計(jì)提高良率。

5. 未來(lái)趨勢(shì)

隨著人工智能和物聯(lián)網(wǎng)的發(fā)展,集成電路CAD設(shè)計(jì)正朝著自動(dòng)化和智能化方向演進(jìn)。機(jī)器學(xué)習(xí)算法被用于優(yōu)化布局,而3D集成技術(shù)則通過(guò)堆疊芯片提升性能。未來(lái),設(shè)計(jì)工具將更注重能效和可靠性,推動(dòng)芯片技術(shù)不斷突破。

集成電路CAD設(shè)計(jì)中的芯片焊盤(pán)和版圖布局是確保芯片功能與質(zhì)量的基礎(chǔ)。通過(guò)合理的設(shè)計(jì)流程和先進(jìn)工具,工程師能夠應(yīng)對(duì)復(fù)雜挑戰(zhàn),實(shí)現(xiàn)高性能集成電路的快速開(kāi)發(fā)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.4tsz7.cn/product/25.html

更新時(shí)間:2026-04-14 23:56:17