集成電路設(shè)計(jì)技術(shù)與工具概述

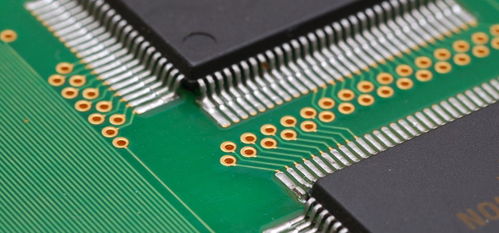

集成電路(IC)設(shè)計(jì)是現(xiàn)代電子工業(yè)的核心環(huán)節(jié),涉及從概念到物理實(shí)現(xiàn)的復(fù)雜流程。本章將系統(tǒng)講解集成電路設(shè)計(jì)的基本技術(shù)、關(guān)鍵工具及其應(yīng)用。

一、集成電路設(shè)計(jì)流程

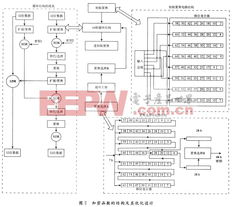

集成電路設(shè)計(jì)通常分為前端設(shè)計(jì)和后端設(shè)計(jì)兩大階段。前端設(shè)計(jì)包括需求分析、架構(gòu)設(shè)計(jì)、RTL編碼和功能驗(yàn)證,確保邏輯正確性;后端設(shè)計(jì)則涵蓋物理設(shè)計(jì)、布局布線、時(shí)序分析和版圖生成,最終輸出可制造的GDSII文件。

二、關(guān)鍵技術(shù)方法

- 硬件描述語言(HDL):Verilog和VHDL是主流設(shè)計(jì)語言,用于描述電路結(jié)構(gòu)和行為。

- 仿真驗(yàn)證:通過軟件仿真和硬件加速驗(yàn)證設(shè)計(jì)功能,常用工具有ModelSim、VCS等。

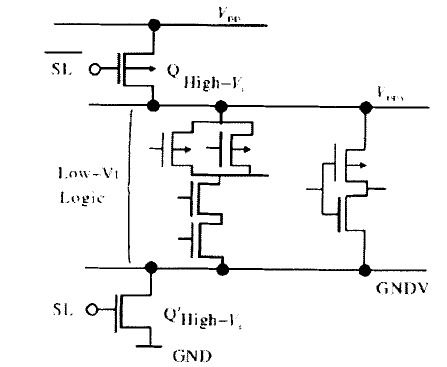

- 邏輯綜合:將RTL代碼轉(zhuǎn)換為門級(jí)網(wǎng)表,考慮時(shí)序、面積和功耗約束。

- 物理設(shè)計(jì):包括布局規(guī)劃、時(shí)鐘樹綜合、布線及DRC/LVS檢查。

三、核心設(shè)計(jì)工具

- EDA工具鏈:Cadence、Synopsys和Mentor Graphics提供全流程解決方案

- 仿真工具:ModelSim、NC-Verilog

- 綜合工具:Design Compiler、RTL Compiler

- 布局布線工具:IC Compiler、Innovus

- 驗(yàn)證工具:Calibre(DRC/LVS)、PrimeTime(時(shí)序分析)

四、發(fā)展趨勢(shì)

隨著工藝節(jié)點(diǎn)進(jìn)入納米級(jí),集成電路設(shè)計(jì)面臨功耗、時(shí)序和可靠性的新挑戰(zhàn)。當(dāng)前技術(shù)正向AI輔助設(shè)計(jì)、3D集成電路和異構(gòu)集成方向發(fā)展,EDA工具也持續(xù)集成機(jī)器學(xué)習(xí)算法以提升設(shè)計(jì)效率。

集成電路設(shè)計(jì)是技術(shù)密集型的系統(tǒng)工程,掌握設(shè)計(jì)方法和工具鏈對(duì)開發(fā)高性能芯片至關(guān)重要。后續(xù)章節(jié)將深入探討各環(huán)節(jié)的具體實(shí)現(xiàn)技術(shù)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.4tsz7.cn/product/29.html

更新時(shí)間:2026-04-14 01:24:17