中規模集成電路功能測試儀的設計與應用

集成電路作為現代電子技術的核心,其可靠性直接關系到整個系統的性能。隨著中規模集成電路(MSI)在通信、計算機、工業控制等領域的廣泛應用,對其功能與性能進行快速、準確的測試變得至關重要。因此,設計一款高效、穩定且易于操作的中規模集成電路功能測試儀,具有重要的工程價值和現實意義。

一、 中規模集成電路功能測試儀的設計目標與原則

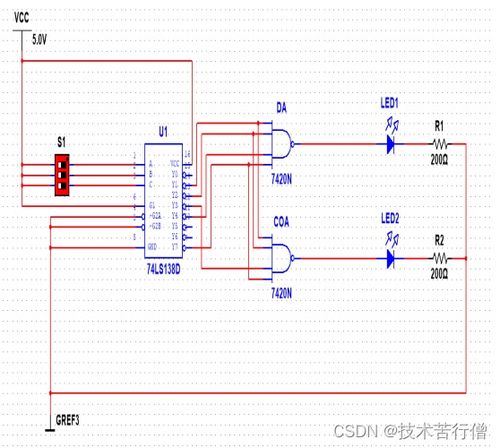

設計一款實用的MSI功能測試儀,首要目標是實現測試的自動化與高覆蓋率。它應能對常見的MSI芯片,如計數器(如74LS161)、譯碼器(如74LS138)、寄存器(如74LS194)、數據選擇器(如74LS153)等進行邏輯功能的完整驗證。設計需遵循以下原則:

- 通用性與可擴展性:測試儀應具備靈活的接口和可編程的測試向量生成能力,以適應不同引腳數和邏輯功能的芯片。

- 高精度與可靠性:測試信號(電平、時序)必須精確,測試結果判定要準確可靠,避免誤判和漏判。

- 操作簡便與高效:提供友好的人機交互界面(如LCD顯示、鍵盤輸入),測試流程應快速,便于生產線或實驗室使用。

- 成本可控:在滿足性能要求的前提下,優化硬件設計,控制整體成本。

二、 系統總體架構設計

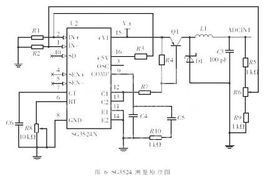

一個典型的MSI功能測試儀通常采用“核心控制器+可編程信號模塊+適配接口+結果分析”的架構。

- 核心控制器:通常采用高性能微控制器(如ARM Cortex-M系列)或FPGA作為系統大腦。MCU方案成本低、控制靈活,適合邏輯相對固定的測試;FPGA方案時序控制精確、并行處理能力強,適合高速或復雜時序的測試。控制器負責執行測試流程、生成控制指令、處理人機交互和分析測試結果。

- 可編程信號模塊:

- 測試向量生成單元:根據待測芯片(DUT)的真值表或功能表,在控制器管理下產生所需的輸入信號序列(測試激勵)。這些數據可預先存儲在存儲器中,或通過算法實時生成。

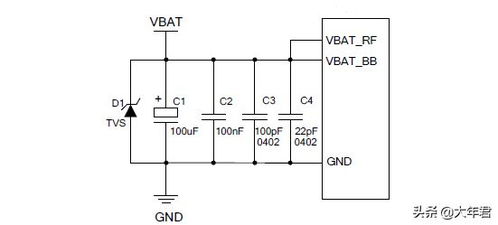

- 精密電源與電平轉換:為DUT提供穩定、精確的VCC和GND,并確保MCU/FPGA的I/O電平(如3.3V)能與DUT的電平(如5V TTL)正確兼容。

- 時序與時鐘電路:產生測試所需的精確時鐘信號和各類控制時序。

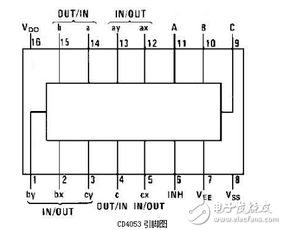

- 適配接口(DUT Socket):這是連接測試儀與待測芯片的物理橋梁。設計需考慮多芯片兼容性,通常采用“通用母座+專用適配板”的方式。適配板上包含必要的上拉/下拉電阻、信號緩沖和引腳映射電路。

- 響應采集與比較單元:實時采集DUT的輸出引腳響應,并將其與預存的“期望響應”(黃金標準)進行比較。比較器電路或軟件算法需考慮建立時間和保持時間,以確保采樣準確。

- 人機交互與通信接口:包括鍵盤、LCD或觸摸屏,用于型號選擇、測試啟動、結果顯示(如“PASS/FAIL”、故障引腳信息)。同時可集成USB、RS232或以太網接口,用于測試程序更新、數據上傳和遠程控制。

三、 關鍵硬件電路設計考量

- 信號完整性:PCB布局布線時,需注意電源去耦、信號阻抗匹配、減少串擾,尤其對于高速測試信號,必要時應采用差分傳輸或屏蔽。

- 過流與靜電保護:在接口電路設計上,需加入限流電阻和TVS管等保護元件,防止因芯片插反、短路或靜電導致測試儀損壞。

- 驅動與負載能力:測試儀的驅動電路需能提供足夠的電流以驅動DUT的輸入引腳;其采集電路需具有高輸入阻抗,以避免對DUT輸出造成過重負載。

四、 軟件與測試流程設計

軟件是測試儀的“靈魂”,其核心是測試程序庫和測試執行引擎。

- 測試程序開發:為每一類MSI芯片開發對應的測試向量集和時序控制流程。這些程序可以基于芯片數據手冊,通過圖形化配置或腳本語言生成。

- 測試執行流程:上電自檢 -> 用戶選擇芯片型號 -> 系統自動加載對應測試程序 -> 通過適配接口連接DUT -> 施加電源 -> 按序施加測試激勵并采集響應 -> 與預期結果逐拍比較 -> 生成并顯示測試報告。

- 故障診斷:對于測試失敗的芯片,軟件應能定位到具體失效的功能點或引腳,提供初步的診斷信息,輔助維修與品控分析。

五、 與展望

中規模集成電路功能測試儀的設計是一個涉及數字電路、微電子、嵌入式軟件和精密測量的綜合性工程。一個優秀的設計需要在硬件精度、軟件智能和用戶體驗之間取得平衡。隨著集成電路向更高集成度、更低電壓和更高速度發展,未來的測試儀設計將更加依賴FPGA和智能算法,并向模塊化、平臺化方向發展,以更靈活地應對日益復雜的測試需求。與計算機輔助設計(CAD)和自動化測試設備(ATE)系統的數據集成,也將是提升測試效率的重要方向。

如若轉載,請注明出處:http://www.4tsz7.cn/product/80.html

更新時間:2026-04-14 11:20:22