基于集成電路CD4053的模擬開關型脈沖分解器設計

在集成電路設計領域,模擬開關型脈沖分解器是一種重要的信號處理模塊,常用于數字系統中對脈沖信號進行分時、分路處理。本文詳細闡述了基于模擬多路復用器/解復用器集成電路CD4053實現的模擬開關型脈沖分解器的設計原理、電路結構、工作過程及關鍵設計要點。

一、設計原理與核心器件

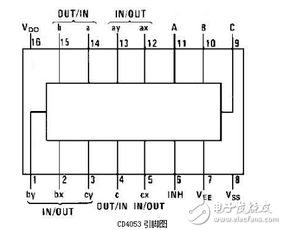

脈沖分解器的核心功能是將一路輸入脈沖信號,根據控制邏輯,分配到多個輸出通道中的某一個。CD4053是CMOS工藝制造的三通道二選一模擬多路復用器/解復用器。其內部包含三個獨立的單刀雙擲(SPDT)模擬開關,每個開關都能雙向傳輸模擬或數字信號。通過控制引腳(A、B、C)的電平狀態,可以精確選擇每個開關的連通路徑。這種特性使其非常適合構建一個基礎的、低成本的多路脈沖分解器。其寬電源電壓范圍(3V至20V)和低靜態功耗,增強了設計的靈活性和實用性。

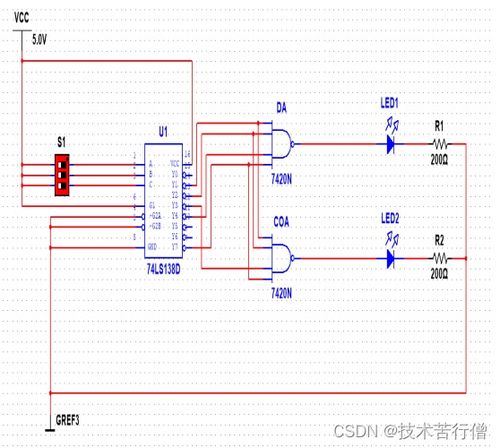

二、電路結構設計

一個典型的基于CD4053的脈沖分解器電路結構如下:

- 信號輸入部分:待分解的脈沖信號接入CD4053的公共輸入/輸出端(例如,三個開關的X公共端分別連接在一起作為總輸入端)。

- 開關陣列:利用CD4053內部的三個開關。每個開關的兩個獨立通道(Y和Z)分別作為一個輸出通道。這樣,單個CD4053理論上可以提供最多6個(3開關×2通道/開關)輸出通道的選擇能力,但通常根據控制邏輯的簡易性,設計為2-3個輸出通道更為常見和直接。

- 控制邏輯部分:這是設計的核心。CD4053的通道選擇由三個獨立的二進制控制引腳A、B、C的電平決定。我們需要設計一個控制邏輯電路(例如,使用計數器、微控制器I/O口或簡單的邏輯門電路),按照預定的時序或外部指令,生成特定的A、B、C編碼,從而在特定時刻將輸入脈沖引導至指定的輸出通道。例如,可以設計一個兩位二進制計數器,其輸出Q1、Q0連接到CD4053的A、B引腳(C接地固定),這樣每四個時鐘周期,輸入脈沖就會在四個可能的輸出通道(對應開關1的Y、Z和開關2的Y、Z)間循環切換,實現一個簡單的順序脈沖分解器。

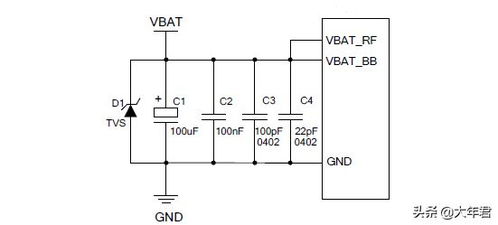

- 使能與電源:必須正確連接使能引腳(INH)。當INH為高電平時,所有開關斷開。正常工作時,INH需接低電平。電源部分需注意為VDD提供正電源,VSS通常接地,VEE在單電源應用中接地,在需要處理負極性信號時可接負電源。

三、工作過程分析

假設設計一個將輸入脈沖Pin分解到兩個輸出通道OUT1和OUT2的簡單電路。我們可以使用CD4053中的一個開關,例如第一個開關(控制端A)。將Pin連接至該開關的公共端X,其Y通道連接OUT1,Z通道連接OUT2。控制端A的電平由外部邏輯提供:當A=0時,開關連通X與Y,脈沖從OUT1輸出;當A=1時,開關連通X與Z,脈沖從OUT2輸出。通過動態改變A端的邏輯電平,即可實現輸入脈沖在兩個輸出通道間的動態分配。增加開關和控制線數量,即可擴展輸出通道數。

四、關鍵設計要點與注意事項

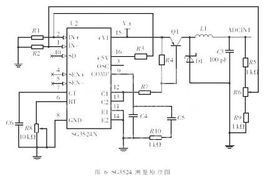

- 信號完整性:CD4053作為模擬開關,其導通電阻(典型值125Ω)和關斷漏電流會影響信號質量,尤其是在高頻或高精度脈沖應用中。需評估其對脈沖邊沿和幅度的影響,必要時可加入緩沖放大器進行整形和驅動。

- 開關速度與帶寬:CD4053的開關速度有限(傳輸延遲時間在數十納秒量級),限制了它能處理的最高脈沖頻率。設計時需確保輸入脈沖的寬度和周期遠大于開關的切換與建立時間。

- 控制時序同步:控制信號(A、B、C)的切換時機必須與輸入脈沖嚴格同步,避免在脈沖持續期間切換通道導致信號被切割或產生毛刺。通常要求控制信號在輸入脈沖的無效期(如低電平期)完成變化并穩定。

- 電源去耦與布局:應在VDD和VSS引腳附近布置良好的高頻去耦電容(如0.1μF),以減少電源噪聲對開關性能的影響。PCB布局時,應盡量縮短信號路徑,特別是高速脈沖走線,以減少分布電容和電感造成的信號失真。

- 電平兼容性:CD4053的控制邏輯電平以電源VDD和VSS為參考。若控制信號來自其他邏輯系列(如TTL),需注意電平匹配,確保在VDD=5V時,CD4053能可靠識別TTL的高、低電平。

五、

基于CD4053設計模擬開關型脈沖分解器,是一種結構簡潔、成本低廉、易于實現的方案。它充分利用了集成電路內部集成的多個高精度模擬開關,通過外部數字邏輯進行靈活配置。盡管在超高速或超高精度場合存在局限性,但對于許多中低速數字系統、教學實驗、儀器儀表通道切換等應用,該設計提供了可靠且高效的解決方案。設計師需要綜合考慮信號特性、速度要求與控制邏輯的復雜性,進行合理的器件選型和電路優化,以確保脈沖分解的準確性和可靠性。

如若轉載,請注明出處:http://www.4tsz7.cn/product/82.html

更新時間:2026-04-14 04:49:37