集成電路基礎 譯碼器與編碼器的應用及1位全減器設計詳解

在數字集成電路設計中,組合邏輯電路扮演著核心角色,其中譯碼器和編碼器是兩種至關重要的基本組件。它們不僅在理論層面構建了數字系統的基石,更在各類實際應用,如數據選擇、地址分配、優先級控制等方面發揮著不可替代的作用。本文將以CSDN博客的技術分享風格,深入探討譯碼器與編碼器的原理與應用,并以此為基礎,詳細闡述如何設計一個經典的1位全減器。

一、譯碼器原理與應用

譯碼器的核心功能是“翻譯”或“激活”。它將一組二進制輸入碼(如地址信號)轉換成一個特定的輸出信號,該輸出信號在眾多輸出線中,只有一條被激活(通常為低電平有效或高電平有效)。

1. 基本原理

一個n位的二進制譯碼器有n個輸入端和2^n個輸出端。對于任何一組有效的輸入組合,只有一個對應的輸出端有效,其余輸出端均處于無效狀態。例如,一個2線-4線譯碼器(如74LS139),當輸入A1A0為“00”時,輸出Y0有效;輸入為“01”時,Y1有效,依此類推。

2. 典型應用

地址譯碼:在存儲器系統(如RAM、ROM)或微處理器接口中,譯碼器用于將CPU發出的地址總線信號轉換為對應存儲單元或外設的片選信號。

指令譯碼:CPU的控制單元利用譯碼器解析操作碼,產生執行指令所需的控制信號序列。

數碼管顯示驅動:將BCD碼(二進制編碼的十進制數)譯碼為驅動七段數碼管各段亮滅的信號。

實現邏輯函數:由于譯碼器的每個輸出端對應一個最小項,配合門電路(如與非門)可以方便地實現任意組合邏輯函數。

二、編碼器原理與應用

編碼器的功能與譯碼器相反,它執行的是“編碼”操作,即將多個輸入信號(通常假設只有一個或少數幾個有效)轉換為一組二進制代碼輸出。

1. 基本原理

常見的有普通編碼器和優先編碼器。普通編碼器(如8線-3線編碼器)要求任何時刻只能有一個輸入有效,否則輸出會混亂。優先編碼器(如74LS148)則解決了這個問題,它為所有輸入信號設定了優先級(通常高位優先),當多個輸入同時有效時,只對優先級最高的輸入進行編碼。

2. 典型應用

鍵盤編碼:計算機鍵盤內部使用優先編碼器,將多個按鍵的按壓信號轉換為對應的ASCII碼或掃描碼。

中斷請求管理:在微處理器系統中,多個外設可能同時發出中斷請求,優先編碼器可以識別優先級最高的中斷源,并將其編碼供CPU處理。

* 數據壓縮與轉換:將特定狀態或事件編碼為更緊湊的二進制形式進行傳輸或存儲。

三、基于譯碼器實現1位全減器設計

全減器是執行帶借位輸入的二進制減法運算的基本單元。它有三個輸入:被減數A、減數B、來自低位的借位輸入Cin;有兩個輸出:差D、向高位的借位輸出Cout。其真值表如下:

| A | B | Cin | D | Cout |

|---|---|------|---|-------|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

設計步驟:

1. 邏輯抽象:根據真值表,我們可以寫出輸出D和C_out的標準與或表達式(最小項之和):

* D = Σm(1,2,4,7)

- C_out = Σm(1,2,3,7)

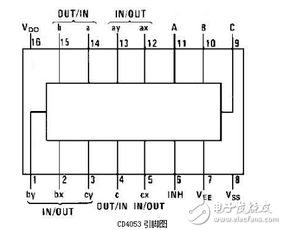

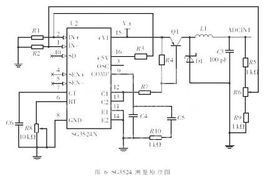

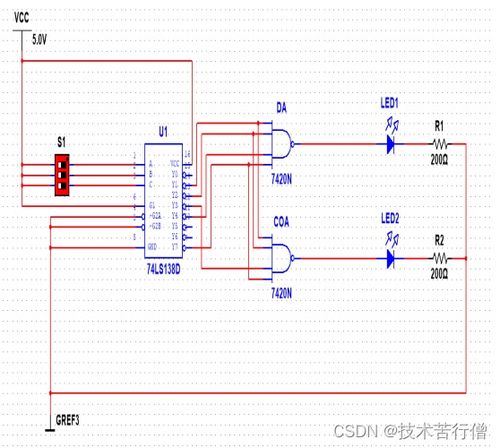

- 器件選擇:選擇一個3線-8線譯碼器(例如74LS138)。它的8個輸出(Y0~Y7,假設低電平有效)分別對應輸入組合A,B,C_in的8個最小項(m0~m7)。

- 電路實現:

- 將全減器的三個輸入A, B, C_in分別連接到譯碼器的三個地址輸入端(如A2, A1, A0)。

- 根據邏輯表達式,差D是m1, m2, m4, m7的邏輯和。由于譯碼器輸出低電平有效,因此需要使用一個4輸入與非門。將譯碼器的輸出Y1, Y2, Y4, Y7連接到與非門的輸入端,與非門的輸出即為差D(D = (Y1'·Y2'·Y4'·Y7')',其中'表示非)。

- 同理,借位Cout是m1, m2, m3, m7的邏輯和。將譯碼器的輸出Y1, Y2, Y3, Y7連接到另一個4輸入與非門的輸入端,其輸出即為Cout。

電路優勢:這種基于譯碼器的實現方法思路清晰,無需進行復雜的邏輯化簡,特別適合用標準中規模集成電路(MSI)快速搭建邏輯功能,體現了模塊化設計的便捷性。對于追求芯片面積和功耗優化的全定制集成電路(ASIC)設計,直接使用化簡后的門級網表(如用異或門、與或非門實現)可能效率更高。

###

譯碼器與編碼器作為數字世界的“翻譯官”,是連接不同數據表示形式的橋梁。通過對它們原理的深刻理解,我們不僅可以將其應用于各種系統級設計,還能靈活運用它們作為“邏輯發生器”來構建更復雜的電路,如本文演示的全減器。在集成電路設計實踐中,掌握這些基本模塊的靈活運用,是邁向更高層次系統設計的關鍵一步。希望這篇分享能為你的學習與實踐帶來啟發。歡迎在評論區交流探討!

如若轉載,請注明出處:http://www.4tsz7.cn/product/81.html

更新時間:2026-04-14 23:58:56